Nano-Micro Letters发表华东师大研究团队最新研究成果

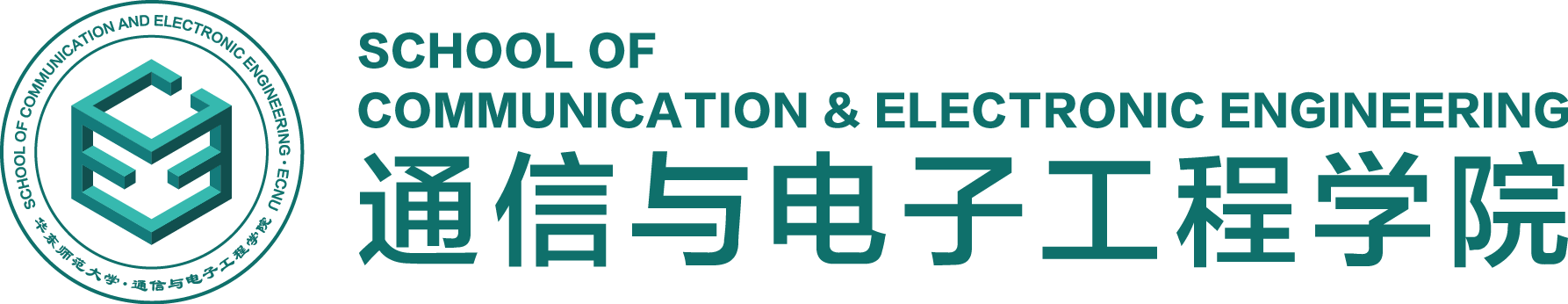

随着半导体技术向1nm节点迈进,传统硅基晶体管因短沟道效应、漏电流激增和三维堆叠工艺复杂度飙升等问题,面临性能和成本的严峻挑战。国际器件与系统路线图(IRDS)虽将硅基互补场效应晶体管(CFET)列为1nm节点的候选技术,但其复杂的三维堆叠结构需成倍增加掩膜数量(图1),导致制造成本剧增。二维材料(如MoS2、WS2)因原子级厚度、高迁移率和优异静电控制能力,被视为突破硅基极限的关键方向。

图1 (a)从16纳米到3纳米以下节点的栅极长度和器件栅极间距的演变;(b)总掩膜数量随技术节点的变化;(c)和(d) MoS2纳米片晶体管的制备流程以及表征图像

近日,华东师范大学通信与电子工程学院(集成电路科学与工程学院)孙亚宾教授团队的沈阳副教授,联合清华大学集成电路学院田禾教授、复旦大学微电子学院的包文中教授,提出基于二维半导体沟道的“等效1 nm”技术方案(“2D eq 1 nm”),即基于纳米片晶体管NSFET工艺引入二维半导体,在性能、功耗和面积上与1 nm节点下的硅基CFET相匹配甚至优于后者,为后摩尔时代芯片技术发展提供了创新性解决方案。

相关成果以“A Valuable and Low-Budget Process Scheme of Equivalized 1 nm Technology Node Based on 2D Materials”为题于2025年3月18日在线发表在Nano-Micro Letters杂志上。华东师范大学集成电路科学与工程学院的孙亚宾教授、清华大学集成电路学院和北京信息科学与技术国家研究中心的田禾教授、复旦大学微电子学院的包文中教授为本论文通讯作者,华东师范大学集成电路科学与工程学院的沈阳副教授为本论文第一作者。

图2显示1 nm(Si),3 nm(2D)和3 nm(2D+)等三个不同节点对应器件版图,其中1 nm(Si)和3 nm(2D+)具有相同的单元占用面积,区别在于前者是CFET结构,而后者采用NSFET。结合第一性原理计算和TCAD搭建跨尺度模拟方法,发现利用二维材料的原子级厚度特性,在材料达到指定的性能指标下,可显著抑制短沟道效应(SS<85 mV/dec,DIBL<120 mV/V),实现高迁移率(200 cm²/(V·s))、高开关比(ION/IOFF=10⁶)和低栅电容(Cgg降低20%)。基于3 nm(2D+)器件搭建16位RISC-V CPU的模拟平台,其频率相比1 nm(Si)提升48%,而工艺结构的复杂度极大降低(从CFET到NSFET),验证了二维材料实现“等效1纳米节点”的可行性(图3)。

二维半导体在先进节点的理论优势使其仍然是下一代半导体的重要候选者。本工作提出二维NSFET工艺取代1 nm节点下的硅基CFET工艺,为二维材料发展成为主流半导体技术提供了有力参考路径。

图2 (a)不同节点的器件面积对比;(b-d)转移特性及反相器VTC特性;

图3基于环振电路和16-bit RSIC-V CPU的系统级性能对比;

附:

论文链接:https://doi.org/10.1007/s40820-025-01702-7